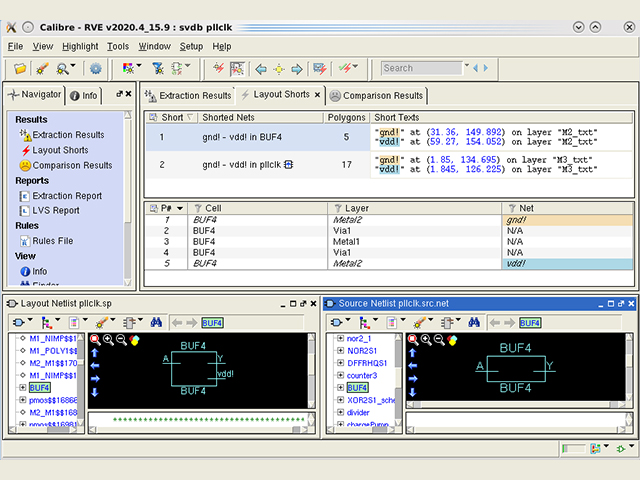

The Calibre nmDRC-Recon use model in Calibre RealTime Digital provides intelligent, automated analysis of immature and incomplete designs across blocks, macros, and full-chip layouts to methodically find and fix high-impact physical layout earlier in the design and verification flow.Calibre RealTime Digital now enables in-design fill with Calibre Yield Enhancer SmartFill, enabling designers to get foundry signoff fill from within their design cockpit, while Calibre RealTime Custom has added the ability to automatically track DRC across multiple regions to enable multiple edits to be fixed, tracked, and checked simultaneously. The Calibre RealTime interfaces provide direct calls to Calibre analysis engines running foundry-qualified signoff Calibre rule decks, helping to improve both design speed and quality of results by providing immediate feedback on design rule violations and recommended rule compliance. The Calibre RealTime Custom and Calibre RealTime Digital software tools, which provide in-design, signoff-quality Calibre DRC for custom, analog/mixed-signal, and digital designs.

Siemens Digital Industries Software announced a range of expanded electronic design automation (EDA) early design verification functionalities for its Calibre platform for integrated circuit (IC) physical verification.Įngineered to help IC design teams and companies get to tapeout faster, these new capabilities are designed to help IC designers "shift left" their physical and circuit verification tasks by moving the identification, analysis, and resolution of complex IC and system-on-chip (SoC) physical verification issues into earlier stages of the design and verification flow.Īmong the new functionalities for the Calibre platform are:

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed